El EzQTrainer, diseñado por Ing. Francisco J. Zamora N., es un circuito totalmente configurable para la enseñanza de conceptos básicos de transistores discretos de todo tipo (especialmente sobre polarización -biasing- y amplificación -small signal-). Fue concebido en el año 2006 y en el 2007 con la colaboración del entonces estudiante Diego Armando Rey tomó forma como un kit ensamblable, con algo de artesanía, en un PCB que se podía acoplar a un protoboard mediante un conector SIL.

Es probable que la idea se siga perfeccionando y en próximos meses se dé a conocer una versión actualizada del sistema que incluya por ejemplo, interfaz a Arduino, o similar y elementos más modernos que permitan reducir aún más su tamaño.

Su forma y tamaño originales se concibieron para poder usar una cajita plástica de los populares dulces TIC TAC como carcasa protectora del circuito entrenador.

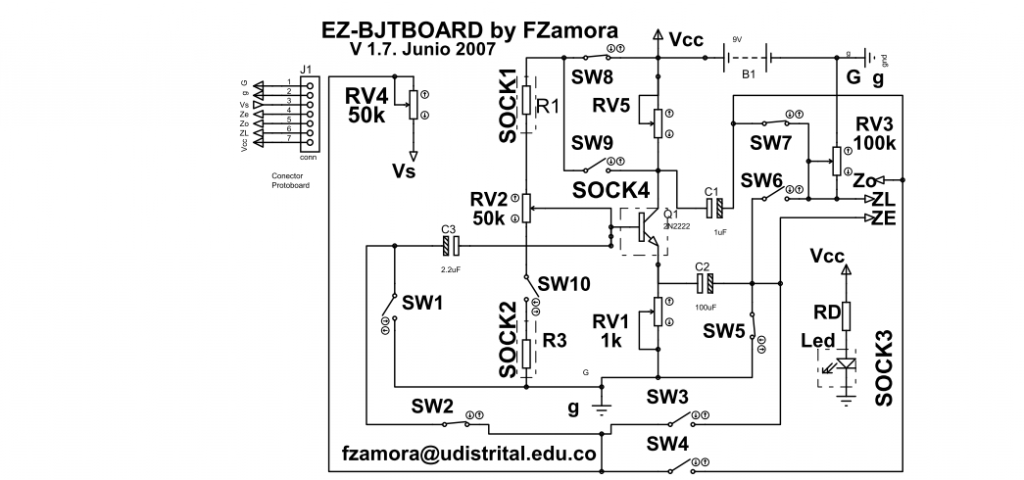

El diagrama eléctrico del circuito, realizado en Proteus VSM, es el siguiente (hacer clic para ampliar):

Aunque el circuito es totalmente funcional sin agregar elementos adicionales, la placa de circuito impreso admite que se puedan colocar resistencias externas (SOCK1 y 2) para obtener valores particulares elevados de resistencia de base o compuerta en polarización, que complementan el reóstato RV2 en placa, así como la inversión de polaridad del LED indicador (en SOCK3) para adaptarse a montajes con transistores PNP o FET canal P (SOCK4) que requieren invertir la polaridad de VCC (convirtiéndose en VDD).

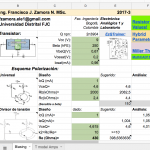

Adicionalmente se ha desarrollado (2017-3) un recurso tipo hoja electrónica en google sheets (una hoja para polarización y otra para configuraciones amplificadoras básicas a partir de modelo T) que permiten agilizar los cálculos para análisis y diseño, verificación de características de configuraciones amplificadoras típicas (según modelo T, ganancias de corriente, tensión, impedancias de entrada-salida) y que el estudiante se centre en los conceptos y la experimentación mediante el ajuste personalizado de parámetros que le permiten observar la estabilidad de los diversos montajes ante cambios y tolerancias de parámetros estandarizados de dispositivos (se recomienda crear una copia en su gdrive bajo su propia cuenta google para poder editar el modelo de referencia):

Haga clic en el enlace –> Hoja de cálculo google sheets para EzQTrainer

También una versión en MathCAD15 de dichos cálculos está disponible como recurso externo desde el mismo enlace indicado, así como algunas otras referencias útiles a sitios web con información tal como valores estandarizados de resistencias, capacitancias, resumen de teorema de Miller, de modelo de parámetros híbridos y modelo T.

También una versión en MathCAD15 de dichos cálculos está disponible como recurso externo desde el mismo enlace indicado, así como algunas otras referencias útiles a sitios web con información tal como valores estandarizados de resistencias, capacitancias, resumen de teorema de Miller, de modelo de parámetros híbridos y modelo T.

Ejemplo de uso:

Para configurar autopolarización o polarización por división de tensión en un transistor NPN con referencia al diagrama eléctrico realizado en Proteus VSM, (por ejemplo 2N3904, colocado en SOCK4) los interruptores SW8 y SW10 estarán cerrados (ON) y SW9 abierto (OFF). En caso de diseño se escogen Vcc, IcQ, VbeQ, Beta (hFE), k1, k2 y VceQ, y se determinan con la hoja de cálculo los valores de Rc (ajustable con RV5) y Re (con RV1). R1 y R2 se seleccionan e insertan de tal manera que, junto con las respectivas secciones del reóstato RV2, conformen los valores más cercanos a los reportados como R1 y R2 por la hoja electrónica de google. El SW5 determina si se desacopla (ON) o no (OFF) Re en el modelo AC para por ejemplo, configuración emisor común (EC). Para colector común Rc (RV5) debería ser cero y para base común SW1 (ON) acopla la base en régimen AC a tierra.

Si se quisiera configurar, por ejemplo, un amplificador base común (BC), un análisis por inspección del circuito en Proteus arroja que se deben colocar en OFF los interruptores SW2, SW4, SW5 y SW6, y en ON los interruptores SW1, SW3 y SW7. La manipulación de los potenciómetros RV4 y RV3 permite determinar Z de entrada o ajustar Z de carga respectivamente.

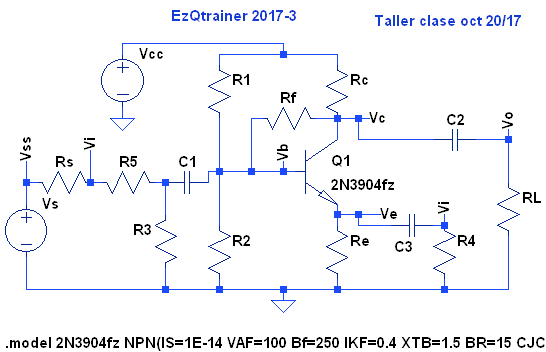

En la imagen anterior se muestra una versión del entrenador de transistores EzQTrainer implementada en el simulador LTSPICE (para Windows, pero se puede ejecutar en MAC OSx y Linux mediante Wine HQ). Dado que este simulador no cuenta con interruptores interactivos (como Proteus), pero es liviano y de uso libre, la configuración personalizada se logra editando los valores de las resistencias (por ejemplo 1.0E-4 para corto circuito y 1.0E+7 para circuito abierto) y renombrando ciertos nodos para interconectar señales: en este ejemplo se renombró el nodo Vi sobre R4 para hacerlo coincidir con Vi entre Rs y R5, lo cual permite aplicar Vs al emisor, R5 y R4 circuitos abiertos y R3 corto circuito, para configurar un amplificador tipo Base Común. Los valores de las capacitancias C1, C2 y C3 se sugieren en la hoja electrónica, para que ofrezcan reactancia mínima a la frecuencia fsmin de la señal de entrada. Es importante determinar en laboratorio los parámetros de los transistores para crear los modelos SPICE adecuados de los mismos (Bf, VAF, Br, IS son algunos de los más importantes para análisis de pequeña señal en bajas frecuencias).

Y los FET?

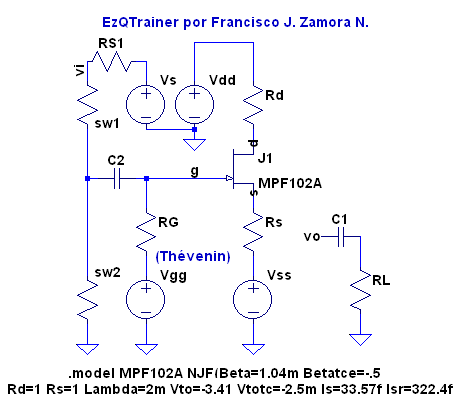

Dado que varios de los esquemas de polarización de BJT son circuitalmente compatibles con los JFET y MOSFET, es posible también usar el EzQTrainer con estos dispositivos. Así mismo se ha dispuesto una hoja electrónica en el enlace indicado anteriormente para cálculos de DC y AC (en Gs, Dc, Sc) con estos dispositivos de efecto de campo. En la siguiente figura se muestra un circuito de referencia para experimentar con JFET en LTSPICE:

En la siguiente versión del EzQTrainer se agregarán algunas configuraciones para soportar la implementación del generador de rampa de voltaje, un módulo que hace parte del dimmer discreto, a su vez, uno de los subsistemas del proyecto del examen final del curso: